Les FPGA peuvent avoir plus de 3000 broches (comme Intel Agilex) qui doivent toutes être connectées sur votre PCB. La conception des FPGA et des PCB est réalisée avec des outils différents, souvent par des ingénieurs différents (et parfois sur des plates-formes matérielles différentes). Vérifier que chaque broche du FPGA est connectée sur la carte de la même manière qu’elle est programmée dans le FPGA est un travail qui prend du temps. Très souvent, cela n’est fait qu’une seule fois dans le processus de conception et après les modifications de conception, les ingénieurs supposent que c’est fait correctement des deux côtés

Du point de vue « PCB »

La conception du circuit imprimé commence par une conception de capture schématique dans laquelle tous les composants (qui seront placés sur la carte) sont placés sur une ou plusieurs feuilles. Pour chaque composant, un ou plusieurs symboles sont utilisés. La plupart des symboles sont limités à environ 40 à 50 broches, donc pour un FPGA avec 1000 broches, 20 symboles sont utilisés. Les symboles sont généralement créés sous une forme générique, ce qui signifie que des noms d’E/S descriptifs (tels que définis par le fournisseur) sont utilisés pour chaque broche. Voici un exemple de conception :

La saisie schématique peut facilement contenir plus de 50 pages (feuilles). Les broches IO utilisateur des symboles FPGA seront connectées à un fil qui porte le nom fonctionnel que la broche obtiendra après la programmation. Les broches d’alimentation (nommées VCCINT, VCCAUX, VCCIO7 etc.) doivent être connectés à la bonne tension, déterminée par l’appareil et les normes IO utilisées sur les broches IO de l’utilisateur. Les FPGA ont jusqu’à 20 groupes différents de broches d’alimentation.

Lorsque tous les symboles sont connectés, un concepteur génère ensuite une netlist. Une netlist est compilée à partir de tous les composants avec toutes les connexions. Il s’agit d’une (longue) liste des combinaisons composants-broches et des connexions qui les relient. C’est le début de la conception physique de la carte. Avant de commencer la conception du PCB, des vérifications approfondies de l’exactitude de la netlist doivent être effectuées. La lisibilité d’un fichier netlist dépend fortement de son format. Il existe souvent des formats d’exportation supplémentaires, plus faciles à lire et à utiliser.

Du point de vue « FPGA »

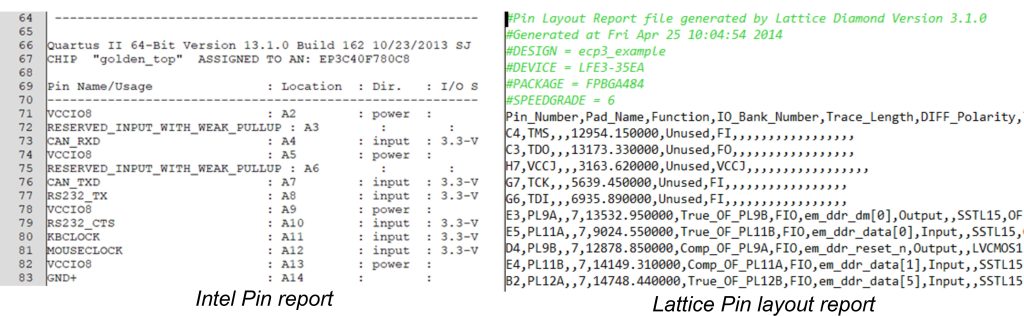

Tous les fournisseurs de FPGA ont une stratégie similaire pour créer le comportement d’un FPGA. Cela commence par une description VHDL ou Verilog (associée à des macros pour des interfaces complexes comme la mémoire DDR ou les interfaces PCIe…) et un ou plusieurs fichiers de contraintes. Les fichiers de contraintes indiquent à l’outil FPGA quels signaux sont affectés à quelles broches et quelles normes IO à utiliser pour une broche. Après le processus de mise en œuvre, les outils génèrent des fichiers du mapping final des broches. Le rapport de broches est une longue liste décrivant les broches, le nom du signal, la norme IO et d’autres fonctionnalités. La qualité de ces fichiers varie beaucoup. Intel et AMD (Xilinx) ont des rapports assez complets, Lattice et Microsemi manquent souvent d’informations sur les broches d’alimentation et de masse.

Certains formats de rapport doivent être modifiés avant d’être importés dans un fichier Excel.

Le processus de vérifcation

Un concepteur (soit le concepteur FPGA, soit le concepteur PCB) doit vérifier que chaque broche FPGA (E/S utilisateur, alimentation, masse et broche de configuration) est connectée au signal correspondant dans la netlist. Il y a 3 approches possibles :

- Manuellement

- Basé sur des scripts

- Basé sur l’utilisation d’un outil

La vérification manuelle

Dans le processus de vérification manuelle, l’ingénieur parcourt toutes les broches du rapport et vérifie la broche correspondante dans la netlist ou sur le symbole de la page schématique. Les rapports de broches E/S sont toujours triés par numéro de broche, il est donc difficile de voir les groupes fonctionnels de signaux (comme ceux des mémoires). C’est une procédure qui nécessite beaucoup de temps

La vérification avec un script

Dans la vérification basée sur des scripts, des scripts sont utilisés (principalement en Tcl ou en Python) pour extraire les informations requises de la netlist et les traduire au format CSV. Ensuite, les données de la netlist CSV et le rapport de broche FPGA sont lus dans Excel et triés par numéro de broche. Les deux sources de données sont rassemblées dans une seule feuille et une comparaison manuelle ou semi-automatisée est effectuée. La quantité de travail manuel dépend sur la qualité des scripts. La comparaison automatique ne fonctionne que lorsque les noms des signaux sont identiques dans chaque environnement. Les broches d’alimentation ne sont généralement pas vérifiées à l’aide de scripts.

La vérification avec l’utilisation du logiciel « IO Checker »

IO Checker de l’éditeur HDL Works offre un certain nombre d’avantages introuvables dans d’autres outils :

- La vérification ne nécessite pas l’exactitude des noms des broches et des signaux. Les signaux tels que « adresse[1] » et « adresse_1 » sont supposés être correctement connectés.

- L’existence d’un éditeur de règles. L’éditeur de règles est utilisé pour faire correspondre des groupes de signaux qui ont des noms différents dans les deux environnements, mais qui sont correctement connectés. par exemple les signaux de mémoire nommés ‘ddr3_a…’ sur le FPGA et ‘ddr3mem_a…’ sur le PCB : ddr3_ad[0 – 31] => ddr3mem_address[0 – 31]. L’éditeur des règles peut également correspondre à des tableaux de signaux mal alignés : address[0 – 15] => address[1 – 16]

- La vérification des alimentations. Pour les broches d’alimentation, le nom du signal connecté à la broche n’est pas important, mais la valeur de tension l’est. IO Checker peut reconnaître que des noms de signaux tels que « P1V2_VDD » ou « +1,2 V_VDD » signifient 1,2 V et comparer la valeur avec le rapport de broche.

- IO Checker peut ne pas tenir compte des résistors ou des condensateurs en série sur les lignes de transmission et utilise ainsi le véritable nom du signal pour la vérification.

- les non-concordances sont tolérées par l’utilisateur. Pour les signaux qui ont un nom différent dans les deux environnements, mais qui doivent être connectés, un indicateur de non-concordance peut être défini et placé par l’utilisateur accompagné d’un commentaire.

D’autres fonctionnalités du logiciel « IO Checker »

- IO Checker peut reconnaître les circuits pull-up / pull-down et le découplage des alimentations.

- Les données du PCB ou les fichiers CSV peuvent être directement importés dans le logiciel, afin de générer les fichiers de contraintes E/S du FPGA.

- Très souvent, l’affectation des broches est modifiée lors de la phase de la conception du PCB (comme l’opération de pin / part swapping), afin d’améliorer la routabilité des pistes, réduisant ainsi le nombre de croisements et de diminuer le délai. Ces modifications doivent être propagées à la fois aux schémas et à la conception du FPGA. La vérification devra être à nouveau réalisée sur la netlist PCB. IO Checker peut retraiter les fichiers sources en quelques secondes, signaler les changements de signaux côté FPGA et côté PCB.

- La visualisation graphique de l’empreinte du FPGA permet de tenir compte des FPGA alternatifs à pin à pin comptable :

2 commentaires sur “Pourquoi utiliser IO Checker ?”

Les commentaires sont fermés.